## SwitchApp

### SwitchApp - The lowest-latency switch for finance

×

- Full-featured 1/10G Layer 2/3 switch -- implemented in FPGA

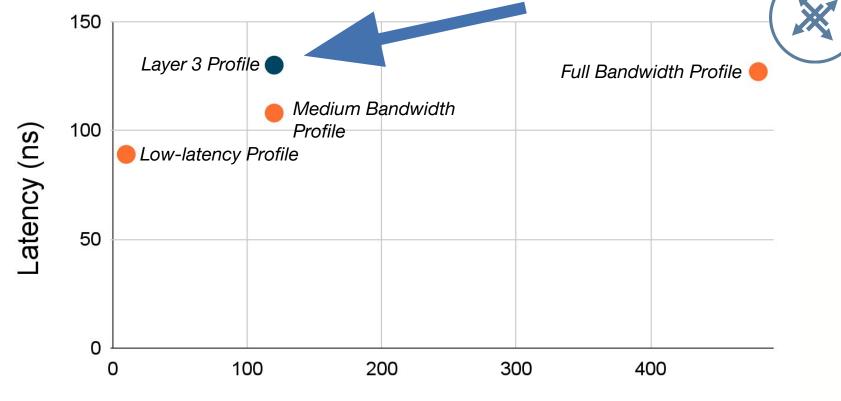

- Ultra-low latency packet forwarding averaging 89\* ns (L2) or 133\* ns (L3)

- Full cut-through architecture

- 48x 1/10G ports

- 10k Uni- or multicast MAC addresses

- 30k unicast, 22k multicast routes

- Fully integrated with EOS, running on 7130LB devices

- Standard EOS CLI and protocols: STP, LLDP, IGMP, LAG

- Standard EOS L3 stack: BGP, PIM, OSPF

- Standard Management, telemetry, protocols, forwarding plane, CloudVision

- Layer 3 features were released in EOS 4.28.0F

- Download at: <a href="https://mako.arista.com/dyn/softwareportal/releases/#switchapp">https://mako.arista.com/dyn/softwareportal/releases/#switchapp</a>

### SwitchApp looks, feels and tastes like any EOS switch

\*NOT STAC BENCHMARKS

### SwitchApp - Updates

- New features released In production now in EOS 4.29.0

- MLAG, VRFs, multicast boundary join control

- Important features coming in Q4:

- PTP Boundary Clock time synchronisation

- LANZ buffer monitoring latency monitoring.

- Routed ACLs

- VRRP

- Watch this space:

- More features coming via software update in Q1. Feedback welcome!

### The features you need, without the baggage.

### Arista SwitchApp – Same Latency, More Features

Bisection Bandwidth (Gbps)

\*NOT STAC BENCHMARKS

### SwitchApp - Now the fastest\* Layer 3 switch too

SwitchApp looks, feels and tastes like any EOS switch

\*NOT STAC BENCHMARKS

### **FPGAs**

### Arista 7130 is an ideal FPGA platform

- Arista 7130 is an enterprise-grade platform for FPGA apps:

- hardware, manufacturing, support, RMAs industry leading.

- o software (e.g. EOS/Linux), security/bug fixes. industry leading.

- engineering cost is amortised across 7130 sales for all use cases.

- Apps are software extensions (e.g. RPM).

- FPGAs are programmed by software. Bitfiles are included in the package.

- Benefits: leverage the platform that we stand behind.

- reduced engineering cost, greater agility.

- trusted by partners and customers for critical applications.

Arista 7130 is a solid foundation for FPGA development.

### Building a development ecosystem

- onlic:

- Our goal: enable developers to write really useful FPGA application.

- Open source example apps

- What we provide:

- An FPGA developer's kit with everything an FPGA team needs to use 7130.

- Examples to copy and modify, IP cores for Arista hardware and networking.

- For higher-layer business logic libraries, talk to our partners.

- Supporting open source

- Recent open-source of pytest-netdut a library for testing software on EOS/MOS.

- Open source example apps in the FDK

- Upcoming open-source release of a buildable FDK

Focussed on enabling FPGA developers

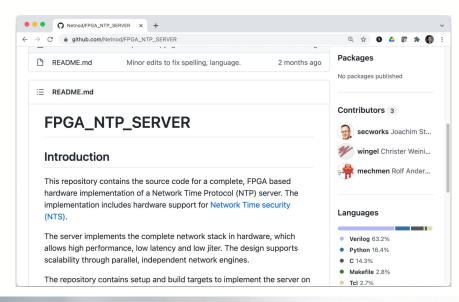

### Open Source Example: Netnod

- Sweden's secure NTP service, delivered by FPGA on Arista 7130

- Open source: <a href="https://github.com/Netnod/FPGA">https://github.com/Netnod/FPGA</a> NTP SERVER/tree/arista

- Moved from homebrew to Arista

- Time sync to PPS, using Arista core

- Uses 7130's OCXO stable oscillator

### How to get started:

- Download the FDK, choose an example, and type "make".

- Have an existing FPGA team and FPGA app?

- Your server: x86 -> PCIE -> FPGA -> Network

- Arista 7130: x86 -> PCIE -> FPGA -> Network

- Port your bitfile to the VU9P FPGA in the Arista 7130 platforms.

- Use Arista's software tools to build operationgal apps.

- Working with a vendor?

- No FPGA knowledge is required to \*deploy\* an FPGA app.

- Third party FPGA vendors are better when strengthened by Arista 7130.

- Just starting out?

- Get in touch with Arista, and we can recommend our partners.

Talk to your team, talk to us at the booth.

# Thank You www.arista.com ARISTA Copyright © Arista 2022. All rights reserved.